NNT/NL: 2022AIXM0446/038ED353

# THÈSE DE DOCTORAT

Soutenue à Grenoble Minatec le 08 décembre 2022 par

## Valentin EGLOFF

Exploration and conception of computing architectures of type computing in-memory based on emerging non volatile memories

#### Discipline

Sciences pour l'Ingénieur

#### Spécialité

Micro et Nanoélectronique

#### École doctorale

ED 353 SCIENCES POUR L'INGENIEUR : MECANIQUE, PHYSIQUE, MICRO ET NANOELECTRONIQUE

#### Laboratoire/Partenaires de recherche

Commissariat à l'Énergie Atomique et aux Énergies Alternatives

### Composition du jury

Gilles SASSATELLI Rapporteur

DR - LIRMM, Université Montpellier

Lorena ANGHEL Rapporteure

PR - Spintec, Grenoble

Mathieu MOREAU Examinateur

MCF - IM2NP, Aix-Marseille Université

Alberto BOSIO Président du jury

PR - INL, Université Lyon I

lean-Michel PORTAL Directeur de thèse

PR - IM2NP, Aix-Marseille Université

Jean-Philippe NOEL Encadrant CEA

PhD - CEA, Grenoble

## **Affidavit**

I, undersigned, **Valentin Egloff**, hereby declare that the work presented in this manuscript is my own work, carried out under the scientific direction of **Jean-Michel Portal**, in accordance with the principles of honesty, integrity and responsibility inherent to the research mission. The research work and the writing of this manuscript have been carried out in compliance with both the french national charter for Research Integrity and the Aix-Marseille University charter on the fight against plagiarism.

This work has not been submitted previously either in this country or in another country in the same or in a similar version to any other examination body.

Grenoble, the 08<sup>th</sup> september 2022,

Cette œuvre est mise à disposition selon les termes de la Licence Creative Commons Attribution - Pas d'Utilisation Commerciale - Pas de Modification 4.0 International.

# List of publications and conference participations

## **Publications made during thesis**

### **Publications**

- **Poster:** "Shuffle operator for matrix multiplication in in-memory computing architecture", **V. Egloff**, Poster in COMPAS, 2019-06, and also in ACACES HiPEAC, 2019-07

- 2<sup>nd</sup> author: J.-P. Noel et al. "Computational SRAM Design Automation using Pushed-Rule Bitcells for Energy-Efficient Vector Processing". In: *2020 Design, Automation & Test in Europe Conference & Exhibition (DATE)*. ISSN: 1558-1101. Grenoble, France, 2020-03, pp. 1187–1192. DOI: 10.23919/DATE48585.2020.9116506

- 2<sup>nd</sup> author: R. Gauchi et al. "Reconfigurable tiles of computing-in-memory SRAM architecture for scalable vectorization". In: *Proceedings of the ACM/IEEE International Symposium on Low Power Electronics and Design*. ISLPED '20. New York, NY, USA: Association for Computing Machinery, 2020-08, pp. 121–126. ISBN: 978-1-4503-7053-0. DOI: 10.1145/3370748.3406550

- 1<sup>st</sup> author: Valentin Egloff et al. "Storage Class Memory with Computing Row Buffer: A Design Space Exploration". In: *2021 Design, Automation & Test in Europe Conference & Exhibition (DATE)*. 2021-02, pp. 1–6. DOI: 10.23919 /DATE51398.2021.9473992

- Maha Kooli et al. "Towards a Truly Integrated Vector Processing Unit for Memory-bound Applications Based on a Cost-competitive Computational SRAM Design Solution". In: *ACM Journal on Emerging Technologies in Computing Systems* 18.2 (2022-04), 40:1–40:26. ISSN: 1550-4832. DOI: 10.1145/3485823. (Visited on 2022-10-04)

#### **Patents**

- **Co-inventeur :** Jean-Philippe Noel et al. "Method and device for designing a computational memory circuit". 2021156420A1. 2021-08

- **Inventeur :** Valentin EGLOFF, Jean-Philippe Noel, and Jean-Michel PORTAL. "Device comprising a non-volatile memory circuit". 4036916A1. 2022-08

## **Conference participations**

- COMPAS, June 2019 in Biarritz, France

- ACACES HiPEAC summer school, July 2019 in Fiuggi, Italy

- Fête de la science, September 2019 in Grenoble, France

- DATE20, March 2020 in Grenoble, France, physical participation **cancelled** due to COVID

- DATE21, February 2021 in Grenoble, France [online]

## Résumé

Les architectures d'aujourd'hui sont basées sur le modèle de von Neumann qui place au centre l'exécution des instructions. Ces architectures font face à de fortes limitations dans le contexte du *big data*. En effet, le mur mémoire est un phénomène lié à l'écart grandissant de performances entre les processeurs et les mémoires depuis les années 80. Pour atténuer cet écart, une hiérarchie de caches a été mise en place mais elle a en contrepartie largement augmentée la consommation énergétique sans être adaptée pour les grands jeux de données modernes. Non seulement ces architectures ont du mal avec une masse de données toujours croissantes à cause de leur haute consommation énergétique et leur faible débit, elles ne peuvent plus uniquement se baser sur les avancées technologiques pour s'améliorer. Ceci appelle à un changement de paradigme vers des architectures *data* centrées où le traitement de quantités de données massives en parallèle est le principe de base.

De nouvelles mémoires non volatiles promettent du stockage haute densité et peuvent intégrer du calcul en mémoire. L'intérêt de calculer en mémoire est d'opérer là où se trouve la donnée, ou tout du moins le plus proche possible, pour supprimer les allées et venues permanentes entre la mémoire et les cœurs de calcul. Les solutions existantes utilisent du calcul analogique très efficace mais prompt au bruit et avec une flexibilité limitée. Quand les données doivent être réécrites en mémoire, l'endurance de ces mémoires non volatiles n'est pas discutée. Nous concevons un emballage numérique qui étend les fonctionnalités mémoire avec du calcul vectoriel et développons une plateforme de simulation pour faire de l'exploration architecturale. Notre circuit, bien nommé C-SRAM, peut être intégré avec la plupart des technologies mémoire et est équipé de sa propre mémoire SRAM. Nous démontrons qu'effectuer le calcul au sommet de la hiérarchie mémoire, c'est à dire proche du stockage permanent, permet une réduction de la consommation énergétique d'un facteur 17.4 et une accélération du traitement en moyenne d'un facteur 12.9 comparé à un traitement avec un cœur SIMD. Grâce à la mémoire tampon intégrée, l'endurance de la mémoire non volatile n'est pas impactée et de fait, l'espérance de vie du système s'en trouve augmentée par rapport à d'autres solutions de calcul en mémoire.

**Mots clés** : calcul en mémoire, mémoire non volatile, architecture des systèmes, mémoire de classe de stockage, mur mémoire, mur énergétique, goulot d'étranglement de von Neumann

## **Abstract**

Today computing centric von Neumann architectures face strong limitations in the data-intensive context of numerous applications. The key limitation is the memory wall due to increased performance gap between processors and memories. To mitigate this gap, cache hierarchy was introduced but it largely increased energy consumption while not being adapted for modern big datasets. Not only those architectures struggle with big datasets due to their high energy consumption and slow bandwidth, they can no longer be improved through technological advances such as node scaling. This calls for a paradigm shift to data centric architecture where treating massive amounts of data in a parallel fashion is the core principle.

New emerging Non-Volatile Memories (NVM) promise high density data storage and can easily integrate In-Memory Computing (IMC). IMC purposes is to compute where the data is or the closest to, to suppress back and forth data movements from the memory to the cores. Existing solutions use analog computing that has high efficiency but limited flexibility. When data needs to be written back after computation, endurance of NVM is often not discussed. We design a digital wrapper that extends memory functionality with vector computing capabilities and develop a simulation platform for architecture exploration. Our digital wrapper, aka C-SRAM, can be integrated with most memory technologies and comes with its own small SRAM buffer. We demonstrate that computing at the top of the memory hierarchy, i.e. close to the permanent storage, grants in average 17.4× energy reduction and 12.9× speed-up versus SIMD baseline. Thanks to SRAM buffer, NVM's endurance is not impaired and thereby extends system lifetime compared to other IMC solutions.

**Keywords**: memory wall, energy wall, von Neumann bottleneck, in-memory computing, non volatile memories, system architecture, storage class memory

## Remerciements

Remarquez, y'a les voisins de mes vieux, ils ont quatre fils, y'en a un il est un peu attardé, et ben c'est leur préféré.

Not all who wander are lost.

— Perceval IN *Kaamelott* BOOK II, EPI-SODE 97, « *Le tourment II* » - J. R. R. Tolkien

Although this thesis is written in english, all my work was done in a french environment, so I will thank people in my native language.

Et voilà, 12 ans après avoir passé mon bac, je finis enfin mes longues études. Études qui ont été un peu erratiques au début avec un passage raté par l'EPFL et une inscription en IUT sous l'impulsion de ma mère. Tout ça pour finir par ne pas si mal rebondir et intégrer l'ENS par la petite porte mais aussi parce que la lumière était allumée. Il en a coulé de l'eau sous les ponts entre mes projets de lycéen de devenir astrophysicien et maintenant en étant bientôt, si <del>Dieu</del> le jury le veut bien ou plutôt m'estime digne de l'être, docteur et rentrer dans la grande famille de la recherche publique française. Cette thèse aura été bien compliquée entre mes quelques problèmes de santé mentale mais aussi parfois physique, et le COVID (viva el COVID) et les confinements associés. J'ai appris à beaucoup relativiser (peut-être même trop) et à ne plus stresser sur des détails dans la vie de tous les jours qui n'ont finalement aucune importance. Avec cette thèse, j'ai beaucoup appris aussi bien humainement que techniquement.

Tout d'abord, je tiens à remercier mes encadrants : **Jean-Michel** et **Jean-Philippe** pour leur très grande patience et leurs conseils avisés. Bien évidemment, sans eux, je ne serais pas là pour écrire ces remerciements. Non pas parce que la thèse ne serait pas tout court, mais parce que j'aurais très certainement abandonné pendant le premier confinement (viva el COVID, *bis repetita*). Mais d'une certaine manière, je pense qu'il m'a aussi permis de finir ma thèse, mais je ne m'explique pas pourquoi j'ai cette impression. Pour **Jean-Michel**, merci pour les conseils scientifiques au sens large : qu'est-ce qui est important, qu'est-ce qui ne l'est pas. Pour **Jean** $\phi$ , merci pour ces échanges sur la culture française, et pas n'importe laquelle, la culture du général de Gaulle. Ensuite, je souhaite remercier les membres du jury pour avoir accepter d'être rapporteur pour ma thèse : **Alberto Bosio**, **Lorena Anghel** et **Gilles Sassateli** et à qui je souhaite évidemment une bonne lecture. Enfin, je remercie également **Mathieu Moreau** pour ses dernières corrections. J'ai l'impression que tu as essayé tous les liens dans ma thèse :).

Je ne peux pas oublier l'équipe avec qui j'ai travaillé pendant ces trois longues années, à moitié enfermé chez nous (viva el COVID, jamais 2 sans 3) : **Bastien**, **Maha** et **Henri-Pierre**. Bienvenue aux petits nouveaux dans l'équipe : **ValentinG**, **Maria** et **Hichem**, j'espère que vous vous y plaisez. Un grand merci spécial pour **Lorenzo** qui m'a beaucoup aidé personnellement et à qui j'ai pu aussi me confier (et réciproquement;)) dans les durs derniers moments de ma thèse.

Merci à tous les gens du labo avec qui j'ai échangé, que ce soit techniquement ou juste pour la discussion autour de la machine à café : Florent, Jean-Fred, Yves, Guillaume, Ivan. Merci à Mariam pour son aide sur le chapitre 3 et le placement routage. Merci à César et Éric pour leur aide sur l'architecture et les caches pour les chapitres 4 et 5. Merci à Manuel qui m'a beaucoup appris sur quasiment tous les outils, pour son super niveau technique et ses discussions toujours intéressantes;). Enfin, un merci spécial aux responsables scientifiques, Yvain (j'attends toujours le gateau au chocolat de ta fille) et Pascal qui malgré leurs agendas de ministre technique avaient toujours du temps à accorder à nous autres, pauvres thésards. Merci à Simone pour son sourire radieux qui illuminait le labo tout entier quand elle passait nous voir, bonne chance dans ta nouvelle carrière. Merci à Marjorie qui m'a accordé un peu de son temps pour être son cobaye quand j'avais besoin d'aide.

Une petite pensée pour tous les jeunes du labo, anciens thésards ou stagiaires que j'ai cotoyé : **Andrea** (merci pour le café), **Thomas** expert vétérinaire en Python, **François** pour les conversations un peu déjantées du midi (et désolé pour les autres autour de la table), **Nicolas** j'espère que ton dos, tes poumons et ta santé vont mieux, **Sota** qui nous a quitté pour la Suisse, **Kevin** et **Mona** avec qui j'ai partagé l'espace ouvert, **Antoine P.** qui vient de débuter sa thèse au CEA, courage tu vas en avoir besoin, **Antoine H.** qui a malheureusement quitté l'aventure doctorale un peu précipitamment (en plus, elle était glaciale) et les autres thésards : **Miguel**, **Manon**, **Paola**, **Housseim** du LGECA et tous ceux que j'ai oubliés (lisez quand même le paragrahe suivant :)).

Un grand merci aux potos avec qui j'ai passé tant de soirées chez eux ou au bar, ma vie à Grenoble ne serait pas grand chose sans vous : **Adrien**, psychologue à ses heures perdues et analyseur de spectre personnalité en ayant un côté suisse (neutre et externe); **Maxence**, marketeux qui a embrassé sa carrière scientifique plutôt que commercial mais qui pourrait vendre du sable à un bédouin; **Stéphane** expert es barbecue et es bricolage; **Roman** qui a essayé tous les bars de Grenoble et toutes les bières dans chaque bar, merci pour tous ces échanges techniques et humains et bon retour parmi nous.

Une dernière chose à remercier et sans quoi aucune recherche dans le monde ne serait possible dans ma conception toute personnelle : la machine à café qui nous a (presque) toujours bien servi.

One last thought for the online people who helped me relax after a hard day of work. Special thanks to **deen** who maintained DDNet tirelessly for almost 10 years now. Thanks to the *old* guys team for the games on fridays or saturdays evening: |Rapture| (you will survive), Sir Skeleton (where are you?), Sir Kruksic (who are you?), Kasia (Weedo is alive), MyStery.Fox. Hello to the dev team: Learath2, heinrich5991, Jupstar ②, Ryozuki, Robyt3 and the newcomer Voxel.

Coucou à toute l'équipe française de TeeWorlds : **Pipou** qui fait survivre la communauté française, **Cireme**, **iParano**, **snailx3**, **cris** aussi membre de l'équipe des *vieux*, la deuxième génération avec **Fluday** seul survivant, et la troisième génération avec **Véna**, **Neben**, **PlantKnight**.

Thanks to all people who contribute to the UNIX systems, Linux and the plethora of (sometimes useless) tools that makes life easier.

# **Table of Contents**

| Af                                                 | fida  | vit                                       | ii     |

|----------------------------------------------------|-------|-------------------------------------------|--------|

| List of publications and conference participations |       |                                           |        |

| Ré                                                 | sun   | né                                        | V      |

| Ab                                                 | stra  | act                                       | vi     |

| Re                                                 | mei   | rciements                                 | viii   |

| Ta                                                 | ble   | of Contents                               | X      |

| Lis                                                | st of | Figures                                   | xiii   |

| Lis                                                | st of | Tables                                    | xvi    |

| Lis                                                | st of | f Listings                                | xvi    |

| Lis                                                | st of | f Algorithms                              | xvi    |

| Lis                                                | st of | f Acronyms                                | xvii   |

| GI                                                 | oss   | ary                                       | ххі    |

| Pr                                                 | eam   | able                                      | 1      |

| 1.                                                 | On    | the semiconductor industry                | 2      |

|                                                    | 1.1   | The end of technology advancement         | 3      |

|                                                    | 1.1   | 1.1.1 Physical limits                     | 3      |

|                                                    |       | 1.1.2 Architecture improvements           | 5<br>5 |

|                                                    |       |                                           | 8      |

|                                                    | 1.0   | 1.1.3 Socioeconomic impacts               |        |

|                                                    | 1.2   | Memory technologies                       | 10     |

|                                                    |       | 1.2.1 Main memory technologies            | 10     |

|                                                    | 1.0   | 1.2.2 Emerging non volatile memories      | 15     |

|                                                    | 1.3   | A new computing paradigm                  | 22     |

|                                                    |       | 1.3.1 Big Data                            | 23     |

|                                                    |       | 1.3.2 Proposed solution: memory computing | 24     |

|                                                    | 1.4   | Conclusion                                | 27     |

| 2.                                                 | Sta   | te of the Art                             | 28     |

|                                                    | 2.1   | Taxonomy                                  | 29     |

|                                                    | 2.2   | Memory computing                          | 30     |

|                                                    |       | 2.2.1 SRAM                                | 30     |

|                                                    |       | 2.2.2 DRAM                                | 33     |

|            |     | 2.2.3 N  | NVM and SCM                                                                                                                                 | 5 |

|------------|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------|---|

|            |     | 2.2.4    | Other works                                                                                                                                 | 0 |

|            | 2.3 | Conclus  | sion                                                                                                                                        | 1 |

| 3.         | CSF | RAM De   | sign 4                                                                                                                                      | 5 |

|            | 3.1 | Motivat  | ions for a digital wrapper                                                                                                                  | 6 |

|            | 3.2 | General  | $1 \operatorname{design} \dots \dots$ | 9 |

|            |     | 3.2.1 S  | Specification                                                                                                                               | 9 |

|            |     | 3.2.2 A  | ALU design                                                                                                                                  | 3 |

|            |     | 3.2.3 P  | Pipeline design                                                                                                                             | 3 |

|            | 3.3 | Experin  | nental results                                                                                                                              | 6 |

|            |     | 3.3.1 V  | <i>N</i> orkflow                                                                                                                            | 6 |

|            |     | 3.3.2 S  | Simulation results                                                                                                                          | 7 |

| 4.         |     |          | platform & Tools 6                                                                                                                          | 3 |

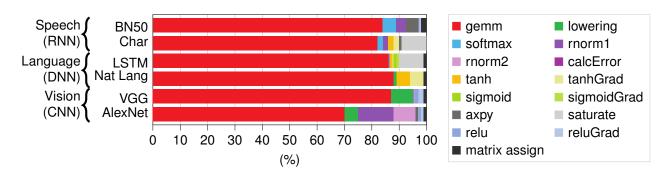

|            | 4.1 | Used be  | enchmarks                                                                                                                                   | 4 |

|            |     | 4.1.1 I  | inear benchmarks 6                                                                                                                          | 5 |

|            |     | 4.1.2    | Quadratic benchmarks 6                                                                                                                      | 5 |

|            |     | 4.1.3    | Cubic benchmarks and real application 6                                                                                                     | 6 |

|            | 4.2 | Existing | g platforms                                                                                                                                 | 7 |

|            |     | 4.2.1 A  | Analytic model                                                                                                                              | 8 |

|            |     | 4.2.2 H  | Hardware counters                                                                                                                           | 8 |

|            |     | 4.2.3 S  | Simulation platforms                                                                                                                        | 0 |

|            | 4.3 | Hardwa   | re model tools                                                                                                                              | 3 |

|            |     | 4.3.1 N  | NVSim                                                                                                                                       | 3 |

|            |     | 4.3.2 I  | DRAM 7                                                                                                                                      | 6 |

|            |     | 4.3.3    | C-SRAM                                                                                                                                      | 7 |

|            | 4.4 | Platforn | <mark>n</mark>                                                                                                                              | 9 |

|            |     | 4.4.1 S  | Software interface for benchmarks                                                                                                           | 9 |

|            |     | 4.4.2 F  | First version with hard coherency                                                                                                           | 2 |

|            |     | 4.4.3 I  | mproved version with soft coherency and real disk accesses . 8                                                                              | 3 |

|            |     | 4.4.4    | Caches and DRAM validation                                                                                                                  | 5 |

| <b>5</b> . | IMC |          | Computing Architectures 9                                                                                                                   | 1 |

|            | 5.1 | Referen  | ce SIMD 512-bit architecture                                                                                                                | 3 |

|            | 5.2 | Compu    | ting at the top                                                                                                                             | 3 |

|            |     |          | Scenario NVM 1: Independent C-SRAM 9                                                                                                        | 4 |

|            |     | 5.2.2 S  | Scenario NVM 2: Computing Row Buffer                                                                                                        | 3 |

|            |     |          | Scenario NVM 1 with page transfer 10                                                                                                        | 4 |

|            |     | 5.2.4 I  | mpact of the reduction loop                                                                                                                 | 5 |

|            | 5.3 |          | ting near DRAM 10                                                                                                                           | 7 |

|            |     | 5.3.1 S  | Scenario DRAM 1: Independent C-SRAM                                                                                                         | 7 |

|            |     | 5.3.2 S  | Scenario DRAM 2: DRAM row buffer 11                                                                                                         | 1 |

|            | 5.4 | Conclus  | gion 11                                                                                                                                     | 2 |

| Conclusion                    | 115 |

|-------------------------------|-----|

| Perspectives and future works | 121 |

| Bibliography                  | 122 |

| Appendices                    | 143 |

# **List of Figures**

| 1.1  | ITRS roadmap as of 2020 and transistor count per chip            |

|------|------------------------------------------------------------------|

| 1.2  | Transistor leakage and gate length evolution                     |

| 1.3  | Predicted scaling cost in 2010 for 2018                          |

| 1.4  | CPU evolution over years                                         |

| 1.5  | CPU and memory performance trends                                |

| 1.6  | Instruction energy breakdown                                     |

| 1.7  | Cost of chips and investment needed                              |

| 1.8  | SRAM bitcell circuit diagram                                     |

| 1.9  | DRAM bitcell circuit diagram                                     |

|      | Example of a DRAM addressing scheme                              |

| 1.11 | Memory hierarchy                                                 |

|      | Die photographs                                                  |

| 1.13 | Different RRAM resistance probability distribution               |

|      | Circuit diagrams of 3 different bitcell types                    |

| 1.15 | Different types of RRAM bitcell                                  |

|      | Different types of PCM bitcell                                   |

| 1.17 | Different types of MRAM bitcell 21                               |

|      | Quantity of data created per year                                |

|      | Internal versus external memory bandwidth                        |

| 1.20 | Memory computing research interest in Google Scholar 26          |

| 2.1  | Taxonomy                                                         |

| 2.2  | Non standard SRAM bitcells used to implement IMC                 |

| 2.3  | DRAM charge sharing using triple row activation                  |

| 2.4  | Coprocessor integrated within NAND Flash SSD                     |

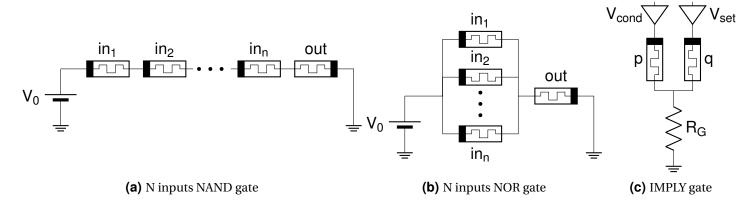

| 2.5  | RRAM boolean gates                                               |

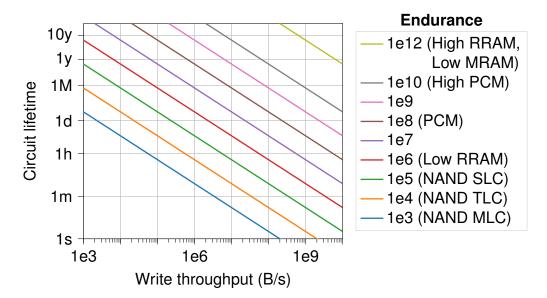

| 2.6  | NVM lifetime for different endurances                            |

|      |                                                                  |

| 3.1  | Proposed design methodology                                      |

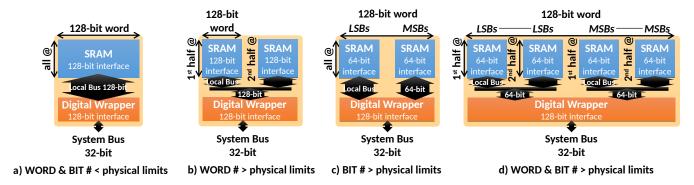

| 3.2  | Different ways of laying out the memories in the C-SRAM 48       |

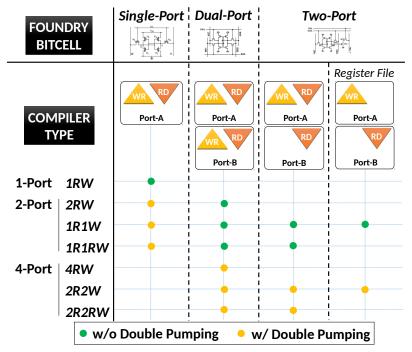

| 3.3  | Potential of the double-pump technique combined with our digital |

|      | wrapper for better pipeline efficiency                           |

| 3.4  | Scalar, vector and scalar/vector computing architectures 51      |

| 3.5  | Defined ISA for 32-bit system                                    |

| 3.6  | Base implementation of our digital wrapper                       |

| 3.7  | Design workflow used for C-SRAM digital wrapper                  |

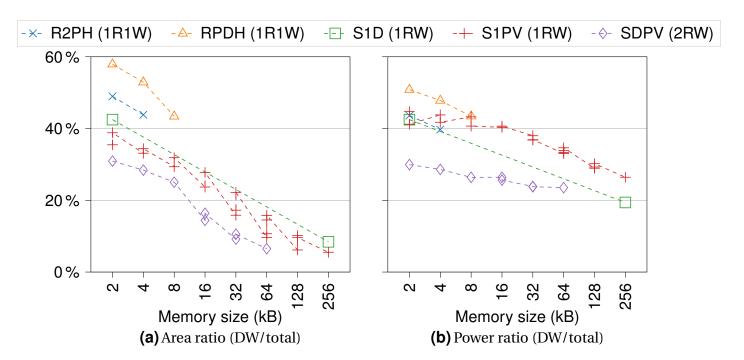

| 3.8  | Area and power overhead for different kind of SRAMs 57           |

| 3.9  | Energy versus delay for MAC instruction                          |

| 3.10 | Throughput comparison of different SRAM types with and without   |

|      | double pump technique                                            |

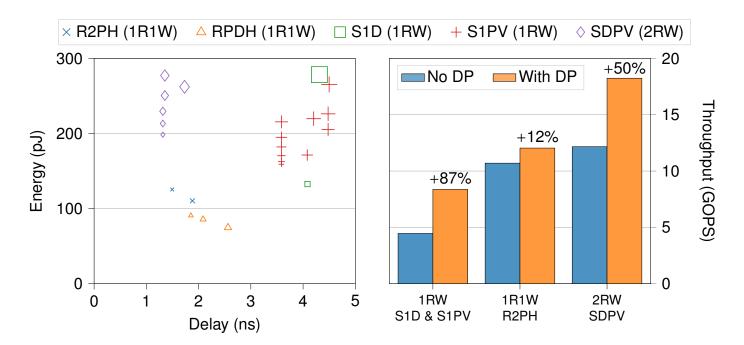

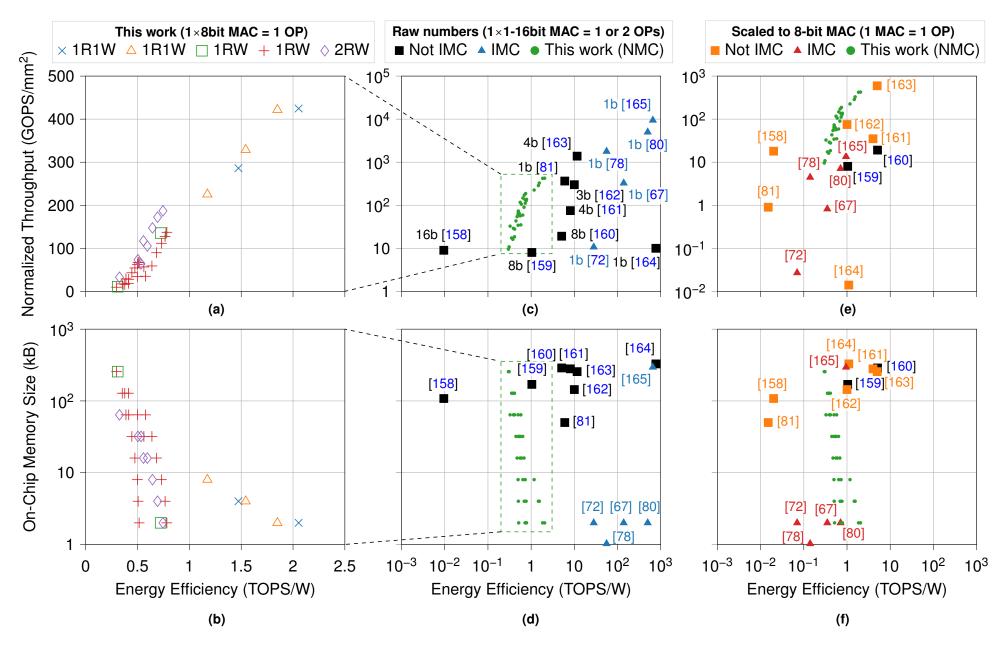

| 3.11       | Throughput and memory size versus efficiency of our solution and                                                                    |     |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | state of the art works on MAC operation                                                                                             | 60  |

| 3.12       | Different place and routed floorplans                                                                                               | 62  |

| 4.1        | Neural network core functions time distribution                                                                                     | 64  |

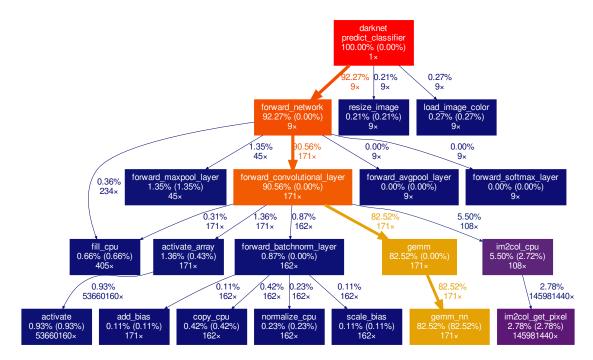

| 4.2        | Darknet callgraph for image classification                                                                                          | 66  |

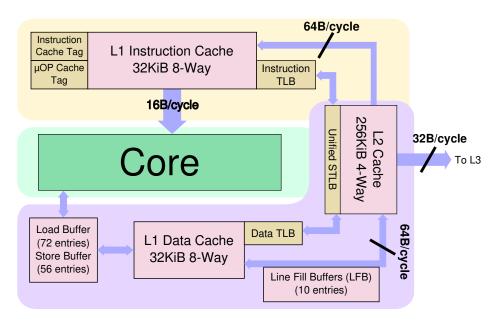

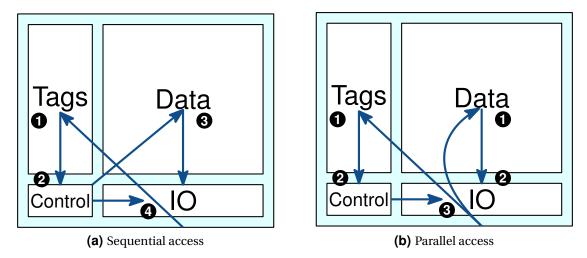

| 4.3        | Simplified view of an Intel Skylake core memory system                                                                              | 69  |

| 4.4        | Cache access types                                                                                                                  | 74  |

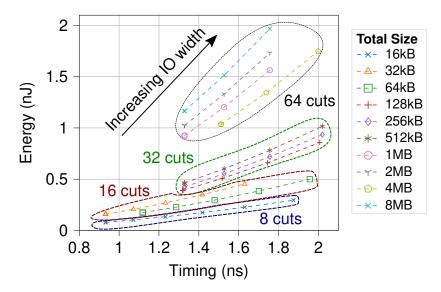

| 4.5        | C-SRAM tiling energy vs timing access costs                                                                                         | 79  |

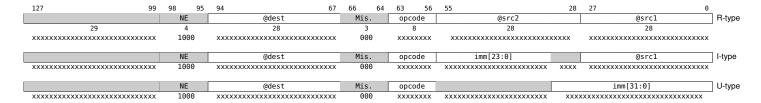

| 4.6        | Extended ISA for 64-bit system                                                                                                      | 81  |

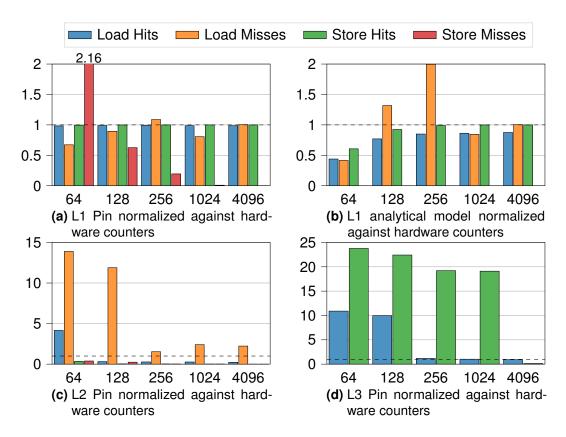

| 4.7        | Our platform normalized against hardware counters for cache events                                                                  | 87  |

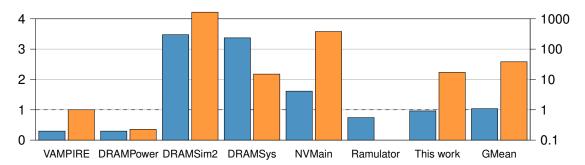

| 4.8<br>4.9 | DRAM tools timing and energy estimation                                                                                             | 88  |

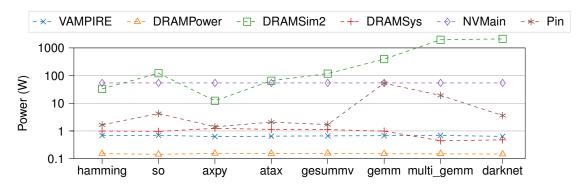

|            | suite                                                                                                                               | 89  |

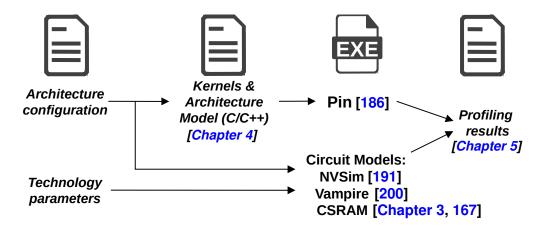

| 4.10       | Workflow used in this thesis                                                                                                        | 90  |

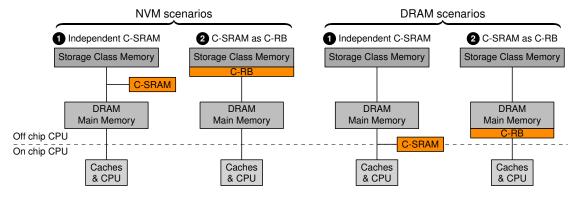

| 5.1        | Different integration possibility of the C-SRAM within the memory                                                                   |     |

|            | hierarchy                                                                                                                           | 92  |

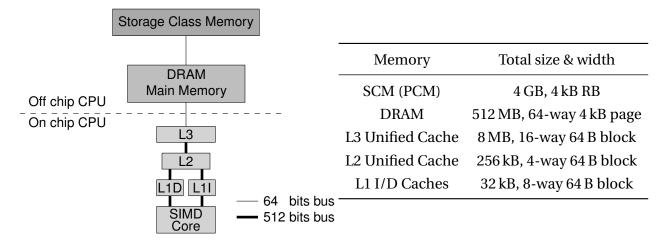

| 5.2        | Reference architecture and memories parameters                                                                                      | 93  |

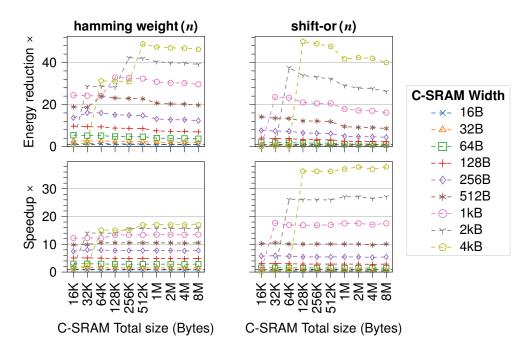

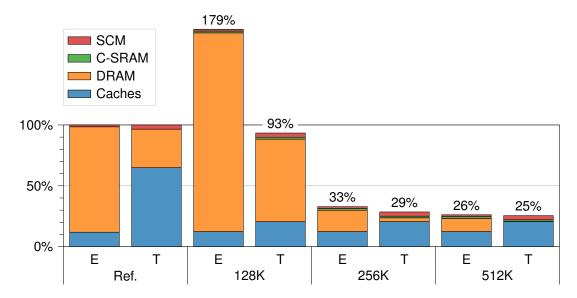

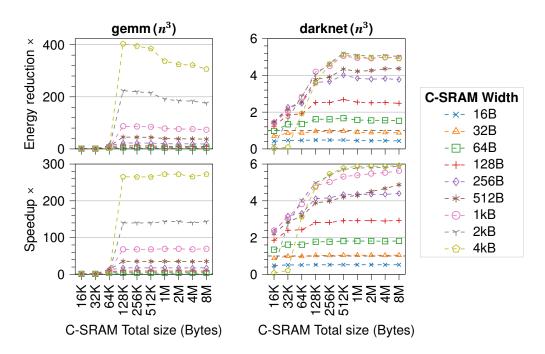

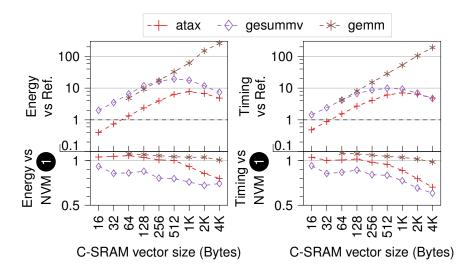

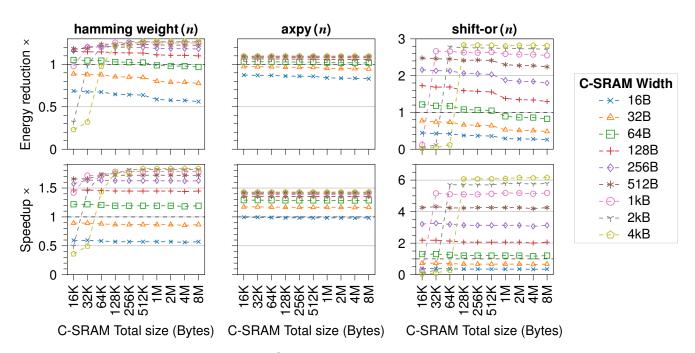

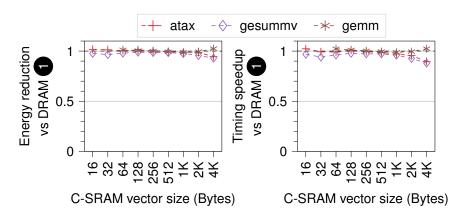

| 5.3        | Scenario NVM 1: Energy reduction and speedup for linear benchmarks normalized against SIMD 512-bit reference                        | 94  |

| 5.4        | Scenario NVM 1: Energy reduction and speedup for linear benchmarks with high SCM access rate normalized against SIMD 512-bit        |     |

|            | reference                                                                                                                           | 95  |

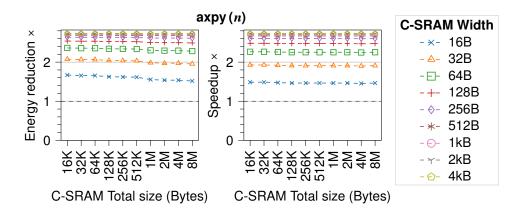

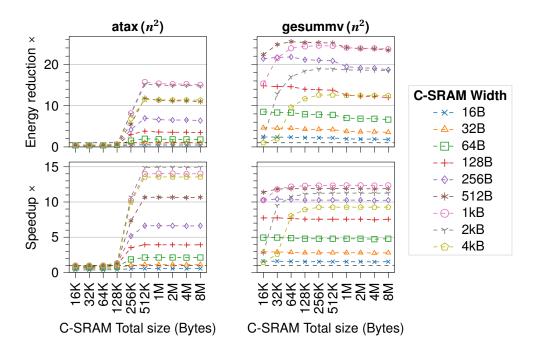

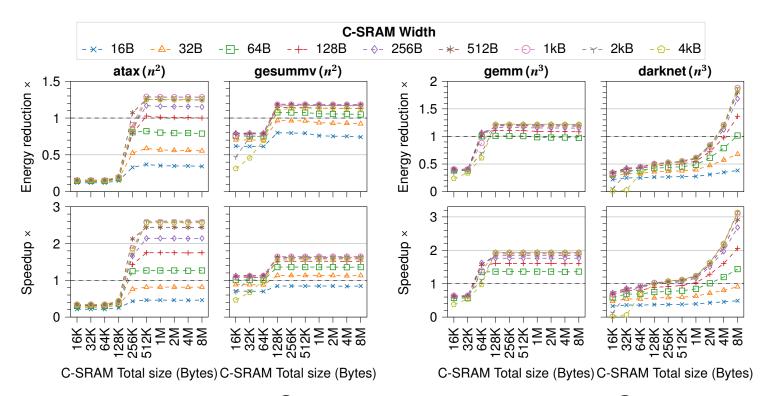

| 5.5        | Scenario NVM 1: Energy reduction and speedup for quadratic bench-                                                                   |     |

|            | marks normalized against SIMD 512-bit reference                                                                                     | 96  |

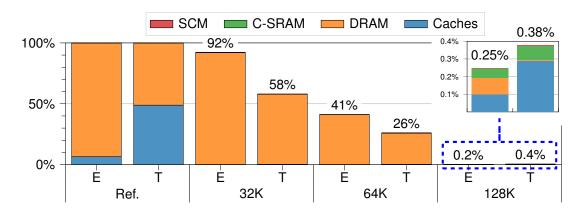

| 5.6        | Relative <i>atax</i> (to SIMD Reference) Energy and Timing distribution for                                                         |     |

|            | different sizes and a vector width of 128 bytes                                                                                     | 97  |

| 5.7        | Scenario NVM 1: Energy reduction and speedup for cubic bench-                                                                       | 00  |

| <b>5</b> 0 | marks normalized against SIMD 512-bit reference                                                                                     | 98  |

| 5.8        | Relative <i>gemm</i> (to SIMD Reference) Energy and Timing distribution for different total C-SRAM sizes and a vector width of 4 kB | 00  |

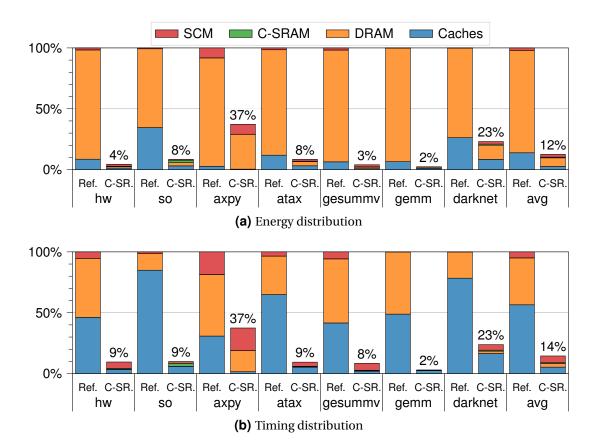

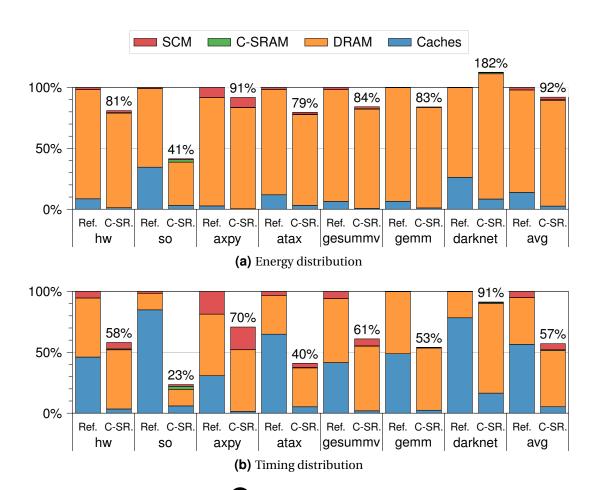

| 5.9        |                                                                                                                                     | 99  |

| 3.9        | Scenario NVM 1: Energy and timing distribution for a C-SRAM of 512 kB and vector size of 512 B normalized to SIMD 512-bit reference |     |

|            | architecture                                                                                                                        | 100 |

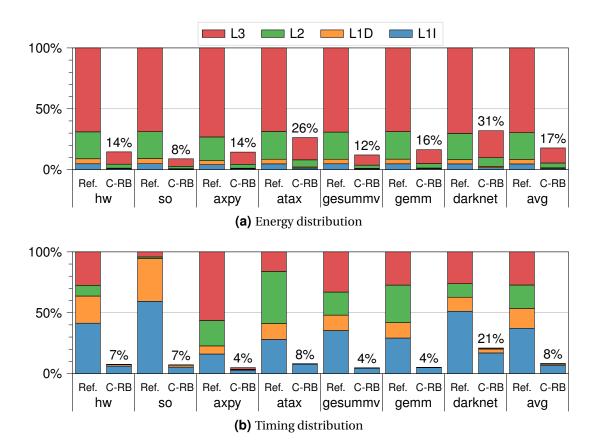

| 5.10       | Scenario NVM 1: Caches energy and timing distribution for a C-                                                                      |     |

|            | SRAM of 512 kB and vector size of 512 B normalized to SIMD 512-bit                                                                  |     |

|            | reference architecture                                                                                                              | 101 |

| 5.11       | SCM memory accesses for a C-SRAM of 512 kB and vector size of                                                                       |     |

|            | 512 B normalized to SIMD 512-bit reference architecture                                                                             | 102 |

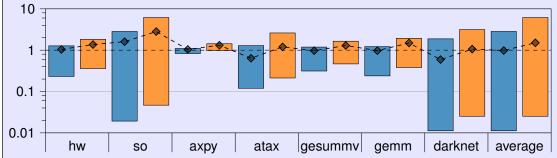

| 5.12       | Scenario NVM 1: Best, worst and average of <i>all</i> cases for both energy                                                         |     |

|            | reduction and speedup normalized against SIMD reference                                                                             | 102 |

| 5 13       | Detailed memory hierarchy for NVM row buffer                                                                                        | 103 |

| 5.14 | Energy reduction and speedup of NVM row buffer scenario 2 nor-               |     |

|------|------------------------------------------------------------------------------|-----|

|      | malized against SIMD reference and independent C-SRAM                        | 104 |

| 5.15 | Energy reduction and speedup of page transfer NVM scenario 1 nor-            |     |

|      | malized against SIMD reference and independent C-SRAM                        | 105 |

| 5.16 | Energy reduction and speedup when performing reduction loop and              |     |

|      | memory broadcast inside C-SRAM compared against the SIMD ref-                |     |

|      | erence and independent C-SRAM scenario                                       | 106 |

| 5.17 | Scenario DRAM 1: Energy reduction and speedup for linear bench-              |     |

|      | marks normalized against SIMD 512-bit reference                              | 108 |

| 5.18 | Energy reduction and speedup for quadratic benchmarks normalized             |     |

|      | against SIMD 512-bit reference                                               | 108 |

| 5.19 | Energy reduction and speedup for cubic benchmarks normalized                 |     |

|      | against SIMD 512-bit reference                                               | 108 |

| 5.20 | Scenario DRAM 1: Energy and timing distribution for a C-SRAM of              |     |

|      | 512 kB and vector size of 512 B normalized to SIMD 512-bit reference         |     |

|      | architecture                                                                 | 110 |

| 5.21 | Energy reduction and speedup when performing reduction loop and              |     |

|      | memory broadcast inside C-SRAM normalized against independent                |     |

|      | C-SRAM at DRAM level (scenario DRAM 1)                                       | 110 |

| 5.22 | Scenario DRAM 1: Best, worst and average of <i>all</i> cases for both energy |     |

|      | reduction and speedup normalized against SIMD reference                      | 111 |

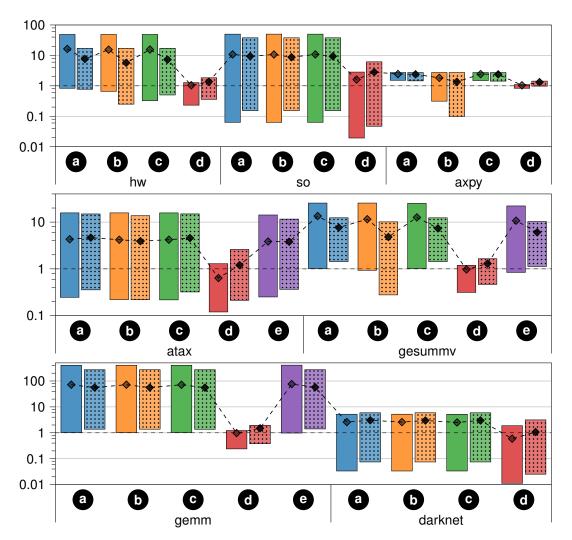

| 5.23 | Minimum, maximum and average for each benchmark and tested                   | 110 |

|      | scenario                                                                     | 113 |

# **List of Tables**

| 1.1<br>1.2<br>1.3                             | Frequency scaling of Intel Xeon core                                                                                                                                   | 6<br>15<br>22                          |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 3.1                                           | Versions used for design workflow                                                                                                                                      | 56                                     |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7 | Benchmarks parameters                                                                                                                                                  | 67<br>71<br>73<br>75<br>76<br>77<br>78 |

| 5.1<br>5.2                                    | Reference architecture memories parameters                                                                                                                             | 93<br>114                              |

|                                               | delay product                                                                                                                                                          | 114                                    |

| Lis                                           | t of Listings                                                                                                                                                          |                                        |

| 4.1                                           | et of Listings  Instrumentation code in Pin                                                                                                                            | 80                                     |

| 4.1<br>4.2                                    | Instrumentation code in Pin C vector types                                                                                                                             | 80<br>81                               |

| 4.1                                           | Instrumentation code in Pin C vector types                                                                                                                             | 80<br>81<br>81                         |

| 4.1<br>4.2<br>4.3                             | Instrumentation code in Pin C vector types                                                                                                                             | 80<br>81                               |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5               | Instrumentation code in Pin C vector types C macro example: 8-bit vector addition Emulation of received instructions                                                   | 80<br>81<br>81<br>81                   |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5               | Instrumentation code in Pin C vector types C macro example: 8-bit vector addition Emulation of received instructions Square matrix multiplication using ikj loop order | 80<br>81<br>81<br>81                   |

# **List of Acronyms**

**ADC** Analog Digital Converter. 31, 35, 39, 42, 44, 46

**AI** Artificial Intelligence. 7, 23, 27, 32–34, 49, 64, 116, 118

**ALU** Arithmetic & Logical Unit. 26, 47, 51, 53–55, 62, 118

**BLAS** Basic Linear Algebra Subprograms. 65, 66, 98, 118

**BRAM** Block Random Access Memory. 7

CAM Content Addressable Memory. 10, 32

**CBRAM** Conductive Bridge Random Access Memory. 18

**CF** Conductive Filament. 18, 19

CIM Computing In-Memory. 29, 33, 38

**CNN** Convolutional Neural Network. 61, 64–67

**CPI** Cycles Per Instruction. 49, 50

**CPU** Central Processing Unit. xxi, 3, 5–7, 10–12, 14, 17, 22, 25, 27,

30-34, 38, 40-42, 52, 53, 65, 69-72, 76, 80, 82, 85, 87, 91, 93,

96, 97, 99–101, 105, 106, 109, 111, 115–121

**C-RB** Computing Row Buffer. 92, 103

**C-SRAM** Computational SRAM. 92

**DBT** Dynamic Binary Translation. 71, 72

**DLP** Data Level Parallelism. 5, 6

**DNN** Deep Neural Network. 39, 61

**DRAM** Dynamic Random Access Memory (see Section 1.2.1.2 for

more details). xxi, 6, 7, 10–17, 19, 21, 22, 24, 26–28, 32–35, 38, 40, 41, 53, 67, 69, 70, 73, 74, 76–78, 82–85, 87–90, 92–99,

101, 103, 104, 107, 109–113, 115, 116, 119–121

| 1 | DSP  | Digital Signal Processor. 7              |

|---|------|------------------------------------------|

| 1 | DVFS | Dynamic Voltage and Frequency Scaling. 5 |

**EDA** Electronic Design Automation. 46, 48

**FPGA** Field Programmable Gate Array. 7, 25, 27, 40, 41

FS Full System. 71, 72

**FSM** Finite State Machine. 47, 54, 55

**GPU** Graphic Processing Unit. 6, 7, 25, 27, 33, 34, 41, 70, 83

**HBM** High Bandwidth Memory. 6, 12, 27, 33, 116

**HDD** Hard Disk Drive (see Section 1.2.1.3 for more details). 6,

11-15, 17, 22, 116

HMC Hybrid Memory Cube. 33, 116

**HPC** High Performance Computing. 8, 11, 42, 43, 89, 93, 120

HRS High Resistive State. 16, 19–21

IMC In-Memory Computing. 1, 17, 23, 25, 26, 28–30, 32–36, 39,

41–46, 48, 49, 59–61, 64, 65, 72, 73, 85, 90, 91, 116–118, 121

**Internet of Things. 2, 23, 38, 43, 49**

IP Intellectual Property. 48

IPC Instructions Per Cycle. 8

IR Intermediate Representation. 72

**ISA** Instruction Set Architecture. xiii, 26, 30, 39, 41, 42, 52–55, 80,

90, 117–119, 121

**LFB** Line Fill Buffer. 69

LIM Logic In Memory. 29, 37

| LLC | Last Level Cache. 69 |

|-----|----------------------|

|     |                      |

**LOP** Low Operating Power. 74

Low Resistive State. 16, 19–21

**LSQ** Load Store Queue. 69

MLC Multi Level Cell. 76

MMU Memory Management Unit. 80

MRAM Magnetic Random Access Memory (see Section 1.2.2.3 for

more details). xx, 18, 21, 22, 39, 74, 117

MTJ Magnetic Tunnel Junction. 21

MVM Matrix Vector Multiplication. 42, 64, 65, 116–118

**NMC** Near-Memory Computing. 26, 29, 30, 32, 35, 40, 41, 48, 72,

73, 116

NMP Near-Memory Processing. 29, 39, 40

**NVM** Non Volatile Memory (see Section 1.2.2 for more details). 1,

15, 20, 22, 27, 35, 40, 41, 43, 44, 48, 49, 62, 72–74, 76, 78, 85,

91–95, 102–105, 107, 109, 111–113, 116, 117, 119, 120

**OoO** Out of Order. xxi, 5, 72

**OS** Operating System. 17, 70, 72, 80

OxRAM Oxide Random Access Memory. 18

**PCM** Phase Change Memory (see Section 1.2.2.2 for more details).

10, 18, 20–22, 39, 40, 48, 73–75, 90, 117, 119, 120

**PCRAM** Phase Change Random Access Memory (see Section 1.2.2.2

for more details). 75

**PIM** Processing In Memory. 29, 33, 34, 37, 40, 41, 116

**PMU** Performance Monitoring Unit. 68, 69

| RAPL | Running Average Power Limit. 70 |

|------|---------------------------------|

|      |                                 |

RAW Read After Write. xxi, 55, 118, Glossary: pipeline hazards

**RRAM** Resistive Random Access Memory (see Section 1.2.2.1 for

more details). 10, 18-22, 36-40, 45, 48, 74, 117

RTL Register Transfer Level. 48

**SA** Sense Amplifier. 10, 11, 16, 25, 31, 35, 38, 42, 116

**SCM** Storage Class Memory. 1, 15, 21, 22, 28, 35, 40, 48, 65, 67,

82-85, 92-96, 99-104, 112, 119-121

SE System Emulation. 71, 72

**SIMD** Single Instruction Multiple Data. 3, 5, 6, 27, 30, 31, 34, 41,

72, 80, 92, 95, 96, 107, 111, 115, 120

SIMT Single Instruction Multiple Threads. 6

SLC Single Level Cell. 35, 36

SRAM Static Random Access Memory (see Section 1.2.1.1 for more

details). 1, 10-16, 18, 19, 21, 22, 25, 26, 28, 30, 32, 33, 35,

38-49, 54, 55, 58, 59, 61, 62, 74, 75, 116-118

SSD Solid State Drive (see Section 1.2.1.4 for more details). 13–15,

17, 20, 35, 40

**STT-MRAM** Spin Transfer Torque MRAM. 21, 39, 40

TCAM Ternary Content Addressable Memory. 31, 39

TTM Time To Market. 46, 48

WAR Write After Read. xxi, Glossary: pipeline hazards

WAW Write After Write. xxi, 55, 118, Glossary: pipeline hazards

# Glossary

| API              | An Application Programming Interface is a particular set of rules and specifications that a software program has to follow to access and make use of the services and resources provided by another particular software program that implements that API. 26, 98                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LRU              | Least Recently Used is a cache replacement policy that replaces the oldest used block in the cache. It is simple yet quite effective. 82, 84                                                                                                                                                  |

| Pipeline Hazards | Occurs when a data is read or written simultaneously at different stages of the pipeline. This is prominent in OoO CPU due to instruction reordering but can also happen in normal pipelines. It includes Read After Write (RAW), Write After Read (WAR) and Write After Write (WAW). 50, 118 |

| Swapping         | Swapping is saving a dirty page from DRAM to disk when the former is full. When the page is needed again, it is loaded back from disk and if the DRAM is still full, another page is saved to disk (i.e. pages are swapped). 83–85, 87, 101, 103, 119, see also thrashing                     |

| Thrashing        | Thrashing is a phenomenon where pages are constantly swapped from DRAM to disk such that the operating system becomes unresponsive. In this thesis, thrashing can also denote the same effect but between DRAM and C-SRAM. 98, 109, see also swapping                                         |

## **Preamble**

Tiens, je ferais bien une partie de quelque chose. Un truc qui se joue vite. On pourrait faire un Sloubi. Je vous explique, y'en a pour 2 secondes.

— Perceval IN *Kaamelott* BOOK III, EPI-SODE 50, « *Perceval chante Sloubi* » To err is human, but to really foul things up you need a computer.

— Paul R. Ehrlich

This thesis is divided in five chapters that will introduce you to the *why* am I doing this thesis: the global context raises issues about computing performances and efficiency that requires an innovating solution (Chapter 1). In-Memory Computing (IMC) is a promising solution compatible with new emerging Non Volatile Memories (NVMs) that also brings new technological improvements in the computer world. We study state of the art in Chapter 2 and show how it misses two key points about NVMs endurance and where to compute in the memory hierarchy. We propose our solution, a digital wrapper around a Static Random Access Memory (SRAM) that we call C-SRAM (Chapter 3). Our C-SRAM can then be tightly coupled to others NVMs or Storage Class Memories (SCMs). To perform an architectural evaluation, we develop a simulation platform fed with technological parameters from state of the art and our own works (Chapter 4). Putting it all together, we show that computing at the top of the memory hierarchy, i.e. close to mass and permanent storage, yields the most gains for both execution time and energy reduction (Chapter 5).

In this thesis, each chapter starts with a *funny* quote from KAAMELOTT, especially from Perceval who will teach you games from Wales country. A more serious quote is also present to give the reader a slight taste of the chapter. Each chapter begins with a small summary of the topics discussed within. You will find some outlines in light blue box (see below) to recapitulate the main points developed in sections and subsections.

I hope you will enjoy reading this thesis as much as I enjoyed writing this final sentence

# 1. On the semiconductor industry

Normalement, ça se joue avec des bouts de bois. Il faut 50 bouts de bois de 2 pouces, 50 de 3 pouces, 50 de 4 pouces et ainsi de suite. Et à la fin, il faut 50 poutres de la longueur de la pièce. Vous avez ça ou pas?

Everything has its limit – iron ore cannot be educated into gold.

— Perceval IN *Kaamelott* BOOK III, EPI-SODE 50 « *Perceval chante Sloubi* » — Mark Twain

Hardware design comes to the end of its golden era where a simple wait of a few months could yield huge improvements for both performance and energy consumption. This was mainly driven by technology scaling and moving to smaller and more advanced nodes. However, as industry reaches the smallest possible node (3 nm), progress can no longer come from technology itself but must come from finer architecture and software designs to better utilize hardware. Famous von Neumann architecture where memories and computing are physically separate and logically distinct units must evolve to face new computing requirements posed by recent rise of big data applications and artificial intelligence. Internet of Things (IoT) devices are also presenting a challenge for energy efficient designs in the wake of societal changes in regard to global warming and energy sobriety.

## **Contents**

| 1.1 | The end of technology advancement |                                     |   |  |  |  |  |  |  |

|-----|-----------------------------------|-------------------------------------|---|--|--|--|--|--|--|

|     | 1.1.1                             |                                     | 3 |  |  |  |  |  |  |

|     | 1.1.2                             | Architecture improvements           | 5 |  |  |  |  |  |  |

|     | 1.1.3                             | 1.1.3 Socioeconomic impacts         |   |  |  |  |  |  |  |

| 1.2 |                                   |                                     |   |  |  |  |  |  |  |

|     | 1.2.1                             | Main memory technologies            | 0 |  |  |  |  |  |  |

|     |                                   | 1.2.1.1 SRAM 10                     | 0 |  |  |  |  |  |  |

|     |                                   | 1.2.1.2 DRAM                        | 1 |  |  |  |  |  |  |

|     |                                   | 1.2.1.3 Hard disk and tapes         | 2 |  |  |  |  |  |  |

|     |                                   | 1.2.1.4 NAND Flash                  | 3 |  |  |  |  |  |  |

|     |                                   | 1.2.1.5 Current memory hierarchy    | 4 |  |  |  |  |  |  |

|     | 1.2.2                             | Emerging non volatile memories      | 5 |  |  |  |  |  |  |

|     |                                   | 1.2.2.1 RRAM                        | 8 |  |  |  |  |  |  |

|     |                                   | 1.2.2.2 PCM                         | 0 |  |  |  |  |  |  |

|     |                                   | 1.2.2.3 MRAM                        | 1 |  |  |  |  |  |  |

| 1.3 | A new                             | computing paradigm                  | 2 |  |  |  |  |  |  |

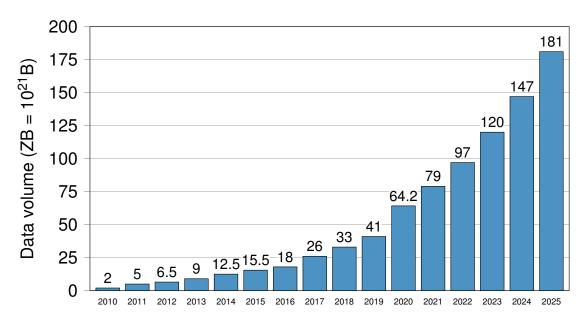

|     | 1.3.1                             | Big Data                            | 3 |  |  |  |  |  |  |

|     | 1.3.2                             | Proposed solution: memory computing | 4 |  |  |  |  |  |  |

| 1.4 | Concl                             | usion                               | 7 |  |  |  |  |  |  |

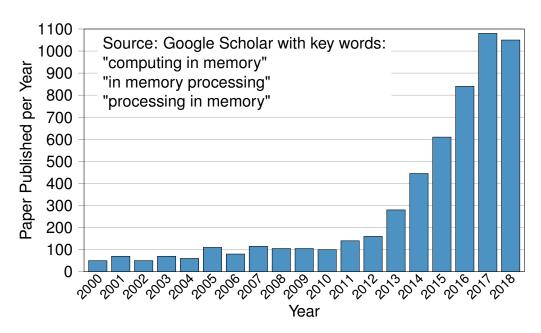

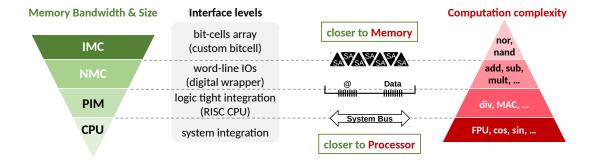

This first chapter will give the reader a very wide introduction and contextualisation on semiconductor technology facing the end of a cycle with a halt to miniaturisation and other well-known obstacles to densification. The key to improve performance is to add more transistors into circuits. However this is defined by physical limits that have been or are being reached nowadays, including energy and memory wall problems (section 1.1). New technologies that may resolve partially these problems are being introduced, especially for emerging memories (section 1.2). These new memories enable a new computing paradigm to solve the admitted von Neumann bottleneck that is exacerbated by big data applications and the rise of artificial intelligence (section 1.3).

## 1.1. The end of technology advancement

## 1.1.1. Physical limits

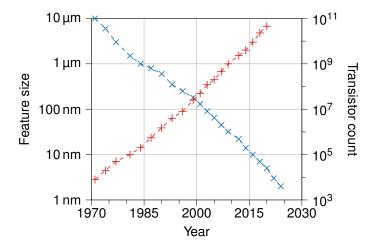

For years, what has driven the semiconductor industry progress is the technology scaling, i.e. the miniaturisation of the transistor. Reducing the transistor, base unit of all the digital world, by a factor of  $\sqrt{2}$  leads to a doubling in the total number of transistors in the same area. Gordon Moore predicted that this doubling would occur every 24 months, later revised down to 18 months. This is known as the Moore's law [1] which held true for almost 50 years (Figure 1.1). More transistors equals more functionalities or more complex ones; as such, we have seen parallel computing emerged during the 2000s with Single Instruction Multiple Data (SIMD) and multicore Central Processing Units (CPUs). However, miniaturisation has limits that cannot be exceeded. It is physically impossible to make a transistor that is smaller than a few atoms and we are already hitting this limit with 3 nm. This means that to answer the growing need for more computing power, semiconductor industry will have to rely on better architectural designs and smarter software models.

**Figure 1.1.:** ITRS roadmap as of 2020 (×, left axis) and transistor count per chip (+, right axis)

#### 1. On the semiconductor industry – 1.1. The end of technology advancement

| Table 1. Technology and circuit projections for processor chip components. |                                        |                       |                       |  |  |  |  |  |

|----------------------------------------------------------------------------|----------------------------------------|-----------------------|-----------------------|--|--|--|--|--|

|                                                                            | 2010                                   | 2010 2017             |                       |  |  |  |  |  |

| Process technology                                                         | 40 nm                                  | 10 nm, high frequency | 10 nm,<br>low voltage |  |  |  |  |  |

| V <sub>DD</sub> (nominal)                                                  | 0.9 V                                  | 0.75 V                | 0.65 V                |  |  |  |  |  |

| Frequency target                                                           | 1.6 GHz                                | 2.5 GHz               | 2 GHz                 |  |  |  |  |  |

| Double-precision fused-multiply add (DFMA) energy                          | 50 picojoules (pJ)                     | 8.7 pJ                | 6.5 pJ                |  |  |  |  |  |

| 64-bit read from an 8-Kbyte static RAM (SRAM)                              | 14 pJ                                  | 2.4 pJ                | 1.8 pJ                |  |  |  |  |  |

| Wire energy (per transition)                                               | 240 femtojoules (fJ)<br>per bit per mm | 150 fJ /bit/mm        | 115 fJ /bit/mm        |  |  |  |  |  |

| Wire energy (256 bits, 10 mm)                                              | 310 pJ                                 | 200 pJ                | 150 pJ                |  |  |  |  |  |

**Figure 1.3.:** Predicted scaling cost in 2010 (45 nm) for 2018 (10 nm). From [4]

Figure 1.2.: Transistor leakage evolution. From [3]

Moving forward to more advanced nodes has also some technical limits that can be seen as side effects for laypeople readers. Smaller transistors are more leaky as the space between different voltage domains is also reduced. On the other hand, it allows to reduce voltage because the threshold voltage is lowered as well. All in one, this leads static power to be dominant in nodes smaller than 90 nm [2] and to increase for each smaller node (Figure 1.2). Moreover, although reducing transistor leads to gain in dynamic power, wire cost is not scaling down with the same tendency. Copper resistivity remains constant and data transit over long wires still stands as the main power sink in every design, especially when memory is on a chip of its own. This is shown in Figure 1.3 dating from 2011 that forecast this difference in power reduction from computing complex operations compared to transmission that will expand four times between 2010 and 2017.

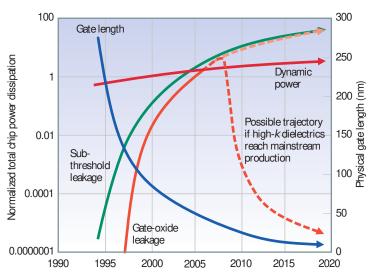

Another problem linked to miniaturisation is Dennard's scaling [5]. It states that as transistors shrink, their power density remains constant. This was true from 1974 to approximately 1995. At that point, power density started to increase (Figure 1.4b) and it ultimately limited frequency increase. Indeed dynamic power is determined by two main factors which are the voltage and the frequency:

$$P_{\rm dyn} = CV^2 f$$

Voltage is fixed by the technology and cannot go below the threshold voltage plus the line loss. C is the parasitic wire capacity swung at every clock cycle and is also a fixed parameter of the technology. So we can only play on the frequency but as we want the most performance, we tend to push it to the maximum acceptable limits by the design, i.e. the maximum power we can either deliver or dissipate. As power density increased, it soon started to be impossible to rise frequency without damaging the circuit hence a frequency saturation from 2005 as shown in Figure 1.4a. These technology problems are physical limits that cannot be broken without a new disrupting technology such as

**Figure 1.4.:** CPUs evolution over years. 2005 Dennard's scaling break is visible in both graph. From [7]

optronic or spintronic that could leverage them. It also led to the famous expression by Herb Sutter: "*The free lunch is over*" [6].

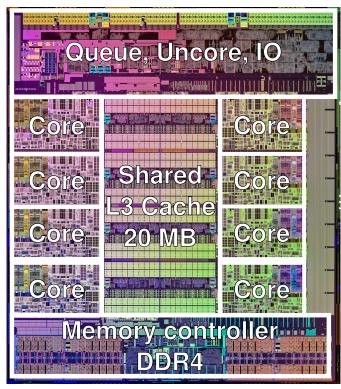

## 1.1.2. Architecture improvements

Industry now faces a double challenge, the impossibility to increase working frequency and the increase in leakage current when moving on to more advanced nodes. To keep performance development in their chips, industries introduced multiple workarounds: Single Instruction Multiple Data (SIMD), multicore and Out of Order (OoO). First, SIMD CPUs were developed to treat multiple data in a single instruction using vector larger (128 bits or more) than the base register (32 or 64 bits at that time). SIMD exploits intrinsic Data Level Parallelism (DLP) in applications. The widest SIMD processor supports up to 512 bits vectors. Secondly, multicore designs permit two independent instruction flows to execute concurrently although they share some hardware, especially memories above L2 or L3 and buses. In some recent commercial chips, up to 64 cores can be used in parallel [8]. Third, OoO CPUs introduction improved compute unit use and reordering of instructions allowed CPUs to mitigate memory timings on independent data paths. With multiple compute units available, processors are said to be superscalar, i.e. capable of executing multiple instructions simultaneously. These three improvements however reached the limit to their computing performances due to power constraint, and insidiously led to the apparition of dark silicon [9]. This happens when complex circuits cannot be fully powered permanently or simply overheat and need to dynamically choose which part to power or to adjust either voltage or frequency using Dynamic Voltage and Frequency Scaling (DVFS). The latter was adopted by the industry because it allowed more flexibility and less stuttering in data streams. An example is given for Intel multicore chips and the use of SIMD extensions in Table 1.1. Dark silicon reveals the low energy efficiency of these designs.

**Table 1.1.:** Frequency scaling of an Intel Xeon Silver 4116, a 12 cores chip, function of active cores and active SIMD extension. From [10]

| Mode   | Base    | Turbo Frequency/Active Cores |         |         |         |         |         |         |         |         |         |         |         |

|--------|---------|------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|---------|

| Wode   | Dase    | 1                            | 2       | 3       | 4       | 5       | 6       | 7       | 8       | 9       | 10      | 11      | 12      |

| Normal | 2.1 GHz | 3.0 GHz                      | 3.0 GHz | 2.8 GHz | 2.8 GHz | 2.7 GHz | 2.7 GHz | 2.7 GHz | 2.7 GHz | 2.4 GHz | 2.4 GHz | 2.4 GHz | 2.4 GHz |

| AVX2   | 1.7 GHz | 2.9 GHz                      | 2.9 GHz | 2.7 GHz | 2.7 GHz | 2.4 GHz | 2.4 GHz | 2.4 GHz | 2.4 GHz | 2.1 GHz | 2.1 GHz | 2.1 GHz | 2.1 GHz |

| AVX512 | 1.1 GHz | 1.8 GHz                      | 1.8 GHz | 1.6 GHz | 1.6 GHz | 1.5 GHz | 1.5 GHz | 1.5 GHz | 1.5 GHz | 1.4 GHz | 1.4 GHz | 1.4 GHz | 1.4 GHz |

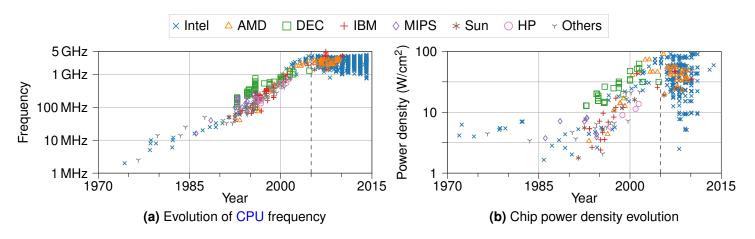

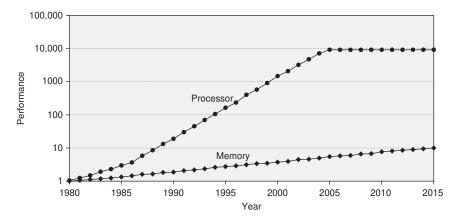

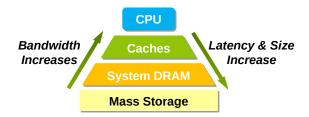

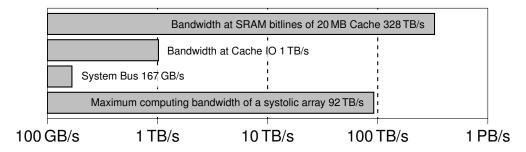

Not only those improvements are not sustainable in the long term, they also put pressure on other system components, typically on the memory system (Figure 1.11). For SIMD, memory now has to serve request up to 512 bits instead of scalar data of 32 or 64 bits. Caches are designed to respond swiftly to these requests but when they would have to serve only a single data, they now have to load large batch of data which increases their power consumption. As vector CPUs treat batch of data, which is now the size of a cache line, caches experience a high miss rate putting more pressure on the slower Dynamic Random Access Memory (DRAM) which becomes the von Neumann bottleneck. This is worsened by multicores because each core will request data to DRAM that the L3 cache cannot store due to its limited capacity. So now, DRAM has to deliver data to several cores simultaneously instead of just one. Each core having its own data set, data locality is reduced which also impacts caches and DRAM performance. This is illustrated in Figure 1.5 where performance of CPUs increase faster than which of memories leading to a performance gap between the computing and the memory systems. This is what is called the memory wall, because the memory cannot deliver data fast enough and the CPU just waits doing nothing. Note that above DRAM, Hard Disk Drive (HDD) and Flash disks have long been surpassed and cannot compete in terms of bandwidth with the need of modern CPUs nor of DRAMs.

To keep increasing throughput and energy efficiency, Graphic Processing Units (GPUs) were pushed in. They use Single Instruction Multiple Threads (SIMT) approach, i.e. different threads all executing same instruction on different data with predicates to allow branches and conditional execution to occur. It heavily simplifies the internal design of the processing elements making them more compact so that thousands can be put on a single chip. This benefits to application with heavy DLP such as filtering an image where the same operation is carried on all pixels with conditional code to handle edge cases. GPUs come with their own main memory, nowadays of type High Bandwidth Memory (HBM) with 256 bits IO and high bandwidth. They also have their own internal caches with 2 levels of cache. Nonetheless, initial data transfer from system main DRAM memory to GPU's memory must still take place before the algorithm runs and data must be sent back once it is done. This back and forth can end up representing more than 90 % of the total execution time depending mainly on the algorithm complexness and the data set size [11]. Overall, GPUs work pretty well on the same regular access patterns as CPUs. They also provide similar program flow with a wide range of complex instructions. Their massive parallelism is used to build some of the Top500 supercomputers [12, 13].

#### 1. On the semiconductor industry – 1.1. The end of technology advancement

Figure 1.5.: CPU and memory performance trends. From [14]

However, both CPUs and GPUs are very generic and can be considered as swiss knives of computing. They do the job but not in a very efficient way except for regular linear access patterns. To improve energy efficiency and throughput, co-processors dedicated to specific tasks were designed, most common one being the Digital Signal Processor (DSP) for embedded systems with real time constraints. Unfortunately, the need for more, better and greener computing requires flexibility that these extra co-processors do not offer. Field Programmable Gate Arrays (FPGAs) are yet another possible mean to gain extra performance by allowing CPU to turn part of itself into a highly energy efficient application specific accelerator and bridge the gap between flexibility of use and efficient designs. Their programmability combined with their natural energy efficiency makes them suitable candidates for use as co-processors. They come with their own memory in the form of Block Random Access Memory (BRAM) with wide IO to feed their natural data level parallelism. Unfortunately, these BRAMs still need to be filled from another external memory which is often DRAM, but FPGAs do improve energy efficiency. So the main problem of memory wall is still there for initial and final data transfer, just like for GPUs. Another step further is using Application Specific Integrated Circuits (ASICs), which are fixed designs but with even better energy efficiency and throughput than FPGAs, but once again, the memory wall remains.

All these hardware solutions are to boost *classic* algorithms performance but there was also the breakthrough of new algorithms in the last decade, mainly Artificial Intelligence (AI) with neural networks. AI is a solution to treat massive amount of data and extract meaningful tendencies but it comes with its own *data* that are the neurons parameters which can also be counted in billions for some networks. Aforementioned hardware solutions can all improve neural networks performances but all end up hitting the memory wall.

The race for best performances, although a great source of hardware improvements such as branch predictors, prefetchers and so on, induced a rising complexity of CPUs that led to some security flaws [15]. But it also drives for more power and ironically reduces energy efficiency [16]. The industry focused on instruction centric paradigm

| Inte   | eger                  | Floating | Point | Memory        |           |  |  |

|--------|-----------------------|----------|-------|---------------|-----------|--|--|

|        | Ado                   | lition   | Cache | 64 bit access |           |  |  |

| 8 bit  | 0.03pJ                | 16 bit   | 0.4pJ | 8kB           | 10pJ      |  |  |

| 32 bit | 0.1pJ                 | 32 bit   | 0.9pJ | 32kB          | 20pJ      |  |  |

|        | Multip                | lication | 1MB   | 100pJ         |           |  |  |

| 8 bit  | 0.2pJ                 | 16 bit   | 1.1pJ | DRAM          | 1.3-2.6nJ |  |  |

| 32 bit | 3.1pJ                 | 32 bit   | 3.7pJ |               |           |  |  |

|        | 25pJ                  | 6pJ      |       | 39pJ          | 70pJ      |  |  |

| I      | I-Cache Register File |          |       | Control lo    | gic Add   |  |  |

|        | access                | acces    | SS    |               |           |  |  |

**Figure 1.6.:** Instruction energy breakdown along with some energy consumption of common instructions and memory accesses. From [17]

where everything was done to increase throughput of instructions, measured in Instructions Per Cycle (IPC). But when looking at the energy bill of simple instructions (Figure 1.6), we see that this is not very efficient as most of the energy comes from moving the data around. With the introduction of *big data* and artificial intelligence applications that uses huge batches of data, this calls for a shift to data centric architectures to solve all the two major challenges: the von Neumann bottleneck aka memory wall and the energy wall or dark silicon.

## 1.1.3. Socioeconomic impacts

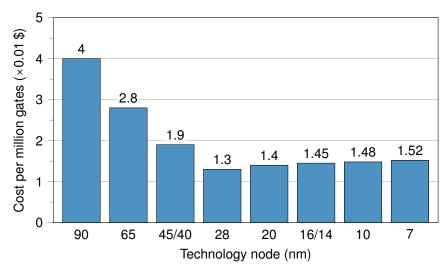

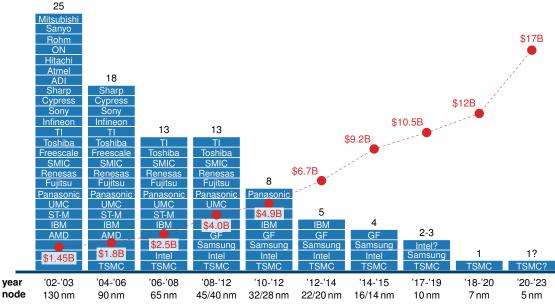

This changing paradigm is in accordance with the evergrowing need for greener computing and better energy efficiency in data centres. High Performance Computing (HPC) centres are reaching tens of megawatt of power consumption which is the equivalent of a 20 000 inhabitants city [12]. Another important point is the economic cost of moving to more advanced nodes which grants no more benefits due to the rising cost of state of the art technologies presented in Figure 1.7. One more part is on water consumption of the semiconductor industry that requires large quantity of extremely pure water which is already a problem due to water shortage in Taiwan. Environmental rejects of different pollutants also need to be accounted for [18].

Up to this point, we have presented the global context and the challenges facing the semiconductor industry for the following years: no more possible scaling, no more power and a growing need for more energy efficient computing. These challenges call for either a shift to different technology or to rethink the architecture of systems to better use them. The best way to reduce energy consumption is to minimize data movement. In the following section, we present the standard memory technologies and the emerging memories that appeared in the last decade.

### 1. On the semiconductor industry – 1.1. The end of technology advancement

(a) Chip cost per million gates (in \$). Cost stopped decreasing after 28 nm in 2012 and slightly increased for following nodes.

**(b)** Founders per node and the associated investment cost (●). High investment cost causes the number of founders to drastically decrease leading to potential monopoly and strategic dependency

**Figure 1.7.:** Cost of chips and investment needed for the founder. The decrease in cost per million gate could finance the investment for the next node before 2012 and the 28 nm node. From [19]

## 1.2. Memory technologies

Previous section dealt mainly with CPUs which is the core of computing systems. We have shown that instruction centric architectures faced a soon to come dead end due to energy and memory walls. This section introduces main memory technologies such as Static Random Access Memory (SRAM) and Dynamic Random Access Memory (DRAM) but also persistent storage to give the reader a broad range of possibilities and perspectives with their associated limitations which represent a major challenge in the data movement cost. Emerging memory technologies including Resistive Random Access Memory (RRAM) or Phase Change Memory (PCM) are presented along with their remaining challenges to make them viable economically and offer substantial benefits for system architects over conventional memories.

## 1.2.1. Main memory technologies

The main memory technologies are the most common ones that can be found in any consumer device. They are the most mature ones and present in the market for decades. However they have some intrinsic design flaws such as high leakage (whether dynamic or static power) or very high latency for non volatiles ones.

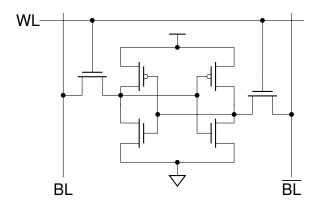

#### 1.2.1.1. SRAM

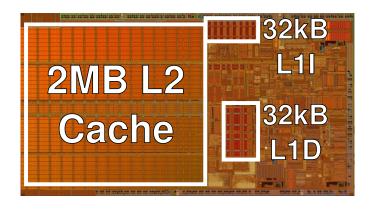

Static Random Access Memory (SRAM) is a fast memory used in almost all existing CPUs dating back to 1964. It provides an extremely fast memory whose working clock frequency is above 1 GHz with virtually infinite endurance. The circuit diagram of a six transistors SRAM bitcell is shown in Figure 1.8. It is made up of two head to toe inverters and two access transistors. Read operation is performed by first precharging the bitlines to  $\frac{V_{\rm dd}}{2}$ , then by activating the two access transistors and using a Sense Amplifier (SA) at the bottom of the bitlines to minimize the error margin. Write operation is done similarly by forcing the data on both bitlines which will switch the state of both inverters. However, the inverters are not perfect and leak, so the SRAM bitcell presents a high static power consumption. It is often arranged in large array, up to 8192 wordlines or bitlines which increases the dynamic consumption due to the large capacitance of the lines. To reduce dynamic switching power, bitlines are often split in local groups with access transistors to commute global bitlines.

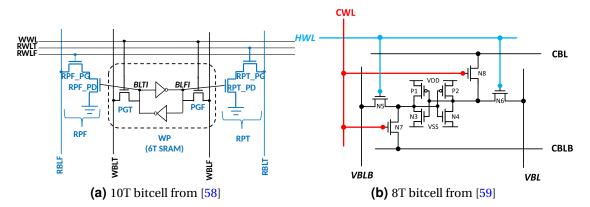

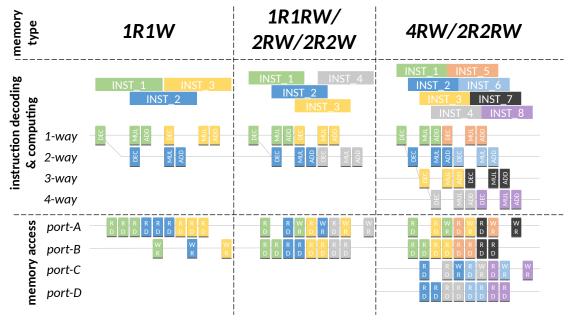

Per se, the 6T bitcell is a 1 read-write (1RW) bitcell, which means that it can either be read or written once per cycle. SRAM bitcell have a large diversity as it also exists in 8T up to 16T. These extra transistors allow to add isolation between the bitcell and the bitlines so that read or write to several bitcells on the same bitline can occur concurrently. This is used to add more access port to the memory to make 1R1W, 1R1RW and even 2RW bitcells. Literature also shows that 6R6W bitcell is possible [20]. SRAM bitcell can also be used as Content Addressable Memory (CAM) memory that is commonly used in routers. Finally, as it is made up of six transistors, it has a very low density that does not allow to have large SRAM memory bigger than a few megabytes.

Figure 1.8.: SRAM bitcell circuit diagram

What makes SRAM so interesting is that it is a CMOS circuit that can be incorporated directly in chips design and scales down along with the technology. It is used as cache or scratchpad memory and is often tightly coupled to CPUs as it is the only memory to keep up the pace with high frequency. Other uses include small buffer memory in devices like HDD, Flash drives or anything that needs few amount of memory before transmitting over serial bus or medium that requires serialisation, e.g. radio transmission. Its flexibility allow designers to easily use custom SRAMs with wide IO or even asymmetrical IO (for serialisation for instance) as well as odd row number.

#### 1.2.1.2. DRAM

Dynamic Random Access Memory (DRAM) is the main volatile memory in non embedded systems such as desktops, servers, HPC and even in some embedded systems like autonomous cars. It features an infinite endurance with medium speed (relative to SRAM) while having a very high density. Figure 1.9 shows the circuit diagram of a DRAM bitcell. It is composed of an access transistor and a capacitor to store the data. This capacitor is leaking so it needs to be refreshed periodically, hence the *dynamic* in the name. This leaking along with the refresh operation cause this memory to have a high dynamic power consumption even when the memory is idle. Read is performed by precharging the bitline to  $\frac{V_{\rm dd}}{2}$  and then by activating the access transistor. The capacitor then discharges or charges the bitline and a SA catches the difference. Read is thus destructive as the capacitor shares its charge with the bitline and the original data needs to be restored. Write is simply done by activating the access transistor and pulling the capacitor to the desired voltage (high for 1, low for 0).

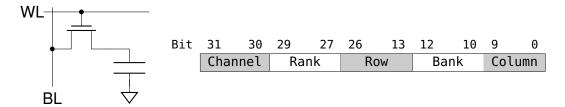

To prevent the whole memory from being inaccessible during a refresh, DRAM is organized in ranks subdivided in chips and in banks. Banks are split across several chips for parallelism reason. Each bank is itself partitioned in subarrays which contain the wordlines and bitlines. Wordlines are referred to as logical rows that spans several chips while bitlines are logical columns. Columns are muxed in a similar fashion to SRAM. To read or write, a DRAM row must first be activated, i.e. selected, it is then loaded in the row buffer where read and write take place for faster operation. In

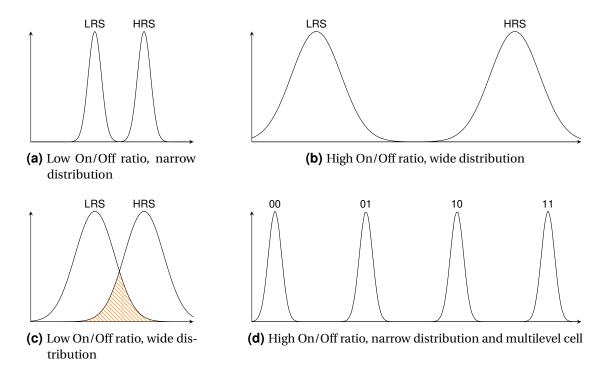

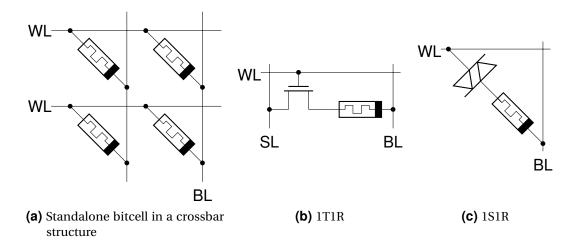

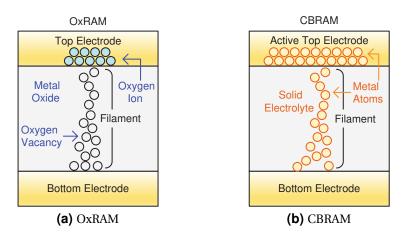

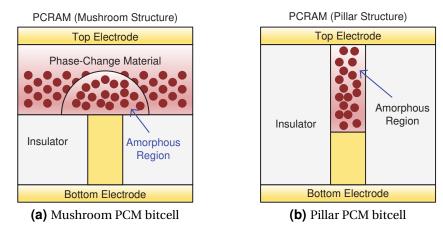

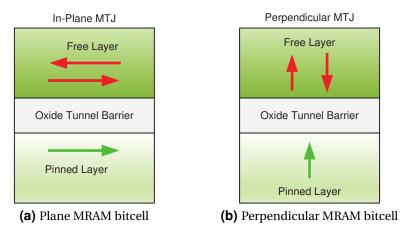

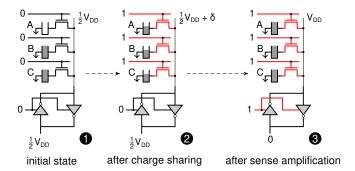

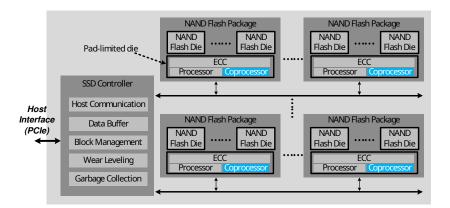

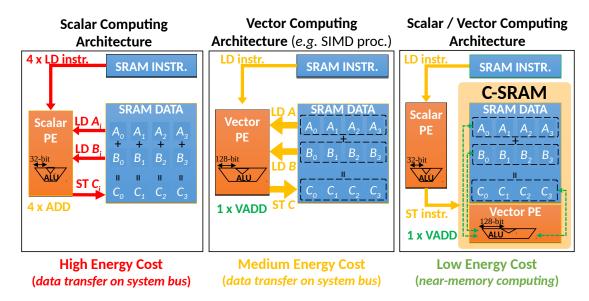

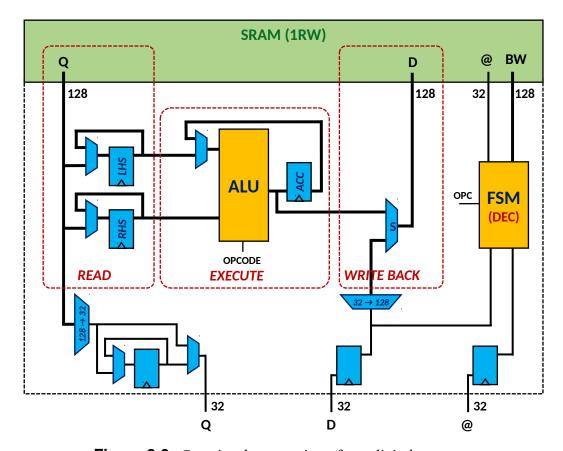

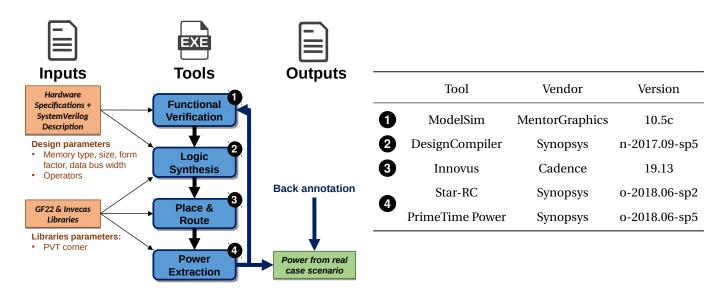

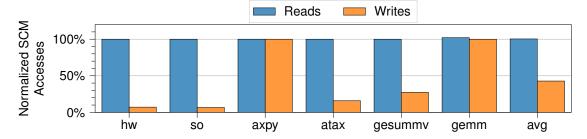

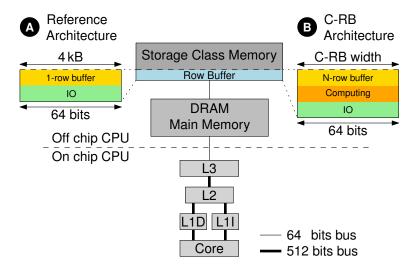

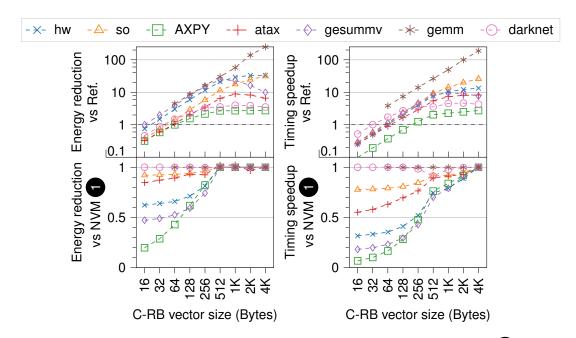

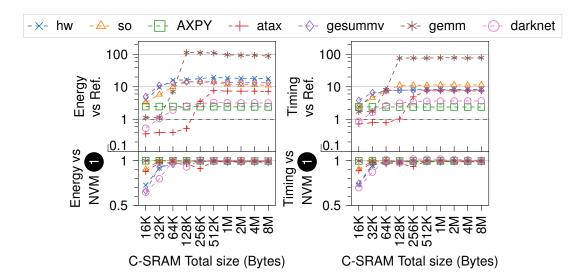

**Figure 1.9.:** DRAM bitcell cir- **Figure 1.10.:** Example of a DRAM addressing cuit diagram scheme